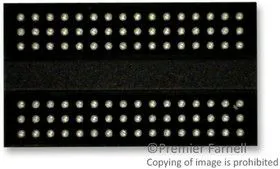

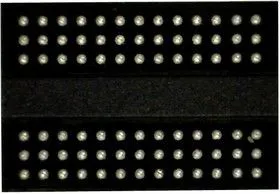

MT47H128M16RT-25E:C, SDRAM, DDR2, 128М х 16бит, 2.5нс, FBGA-84

1 400,00 ₽

Ускоренная память DDR2 с объёмом 128МБ и скоростью 2.5нс, идеальна для быстродействия в системах с высокими требованиями. Купить от FedExpert

MT47H128M16RT-25E: C является DDR2 SDRAM памятью. Для достижения высокоскоростной работы устройство памяти использует архитектуру с двойной скоростью передачи данных. Архитектура с двойной скоростью передачи данных представляет собой архитектуру 4n-prefetch с интерфейсом, который предназначен для передачи двух слов данных за такт на I/O. Одна операция считывания или записи для DDR2 SDRAM состоит из одной 4n-разрядной передачи данных с двухтактным циклом на внутреннем ядре DRAM и четырех соответствующих потоков данных в n-бит с полутактным циклом на I/O. Двунаправленный строб данных (DQS, DQS#) передается извне вместе с данными для использования при захвате данных в приемнике. DQS — это строб, передаваемый DDR2 SDRAM во время считывания и контроллером памяти во время записи. DQS выравнивается по краям с данными для считывания и выравнивается по центру с данными для записи. Предложение x16 имеет два строба данных: один для нижнего байта (LDQS, LDQS #) и один для верхнего байта (UDQS, UDQS

• VDD = 1.8В ±0.1В, VDDQ = 1.8В ±0.1В

• JEDEC стандарт 1.8В I/O (совместимость с SSTL_18)

• Опция дифференциального строба данных (DQS, DQS#)

• Архитектура 4n-bit Pre-fetch

• Опция дублирующего выходного строба (RDQS) для х8

• DLL для выравнивания переходов DQ и DQS с CK

• 8 внутренних банка памяти для параллельной работы

• Программируемая задержка CAS (CL)

• Программируемая Posted CAS дополнительная задержка (AL)

• Задержка записи = задержке считывания — 1 tCK

• Программируемая длина пакета данных 4 или 8

• Регулируемая мощность передачи данных

• 64Мс, обновление 8192 цикла

• ODT

• Поддерживает спецификацию JDSEC Clock Jitter

Полупроводники — МикросхемыПамятьDRAM

Технические параметры

| Минимальная Рабочая Температура | 0 C |

| Максимальная Рабочая Температура | 85 C |

| Количество Выводов | 84вывод(-ов) |

| Время Доступа | 2.5нс |

| Конфигурация памяти DRAM | 128М x 16бит |

| Стиль Корпуса Микросхемы Памяти | FBGA |

| Вес, г | 4.509 |